# 15EC61

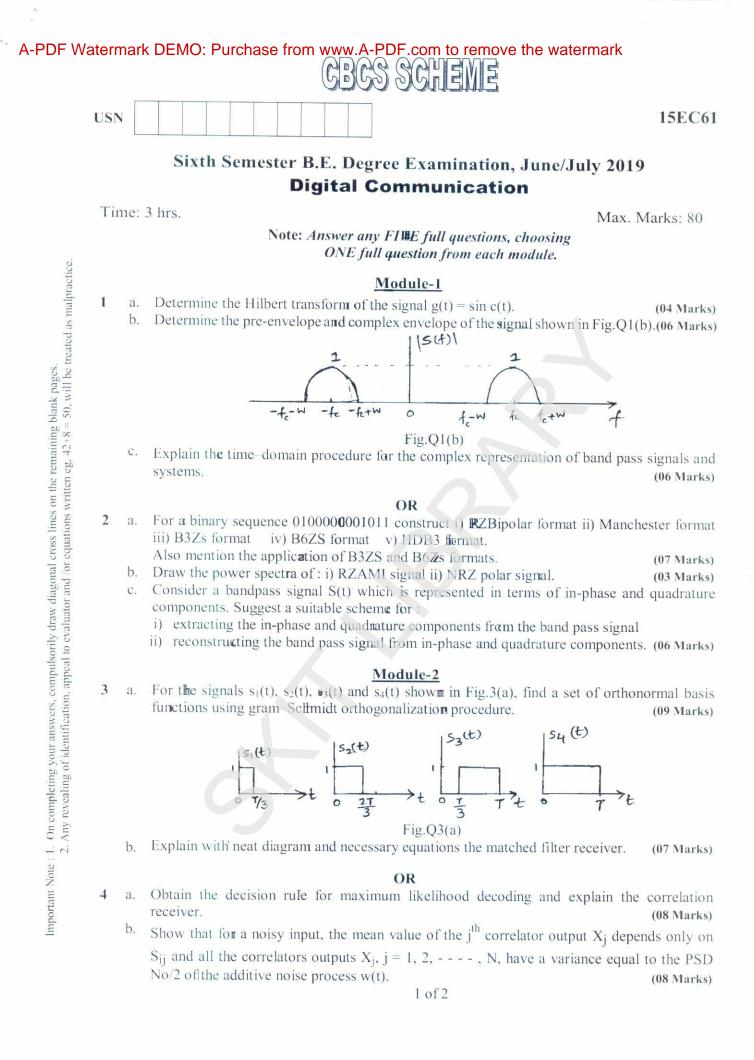

(06 Marks)

(06 Marks)

(10 Marks)

#### Module-3

- a. Sketch the QPSK wave form for the sequence 01101000. 5

- b. Obtain the expression for average probability of symbol error for BPSK using coherent detection. (06 Marks)

- c. Obtain the constcleation of QAM for M = 16 and draw the signal space diagram. (04 Marks)

#### OR

- Explain the generation and coherent detection of BFSK system. 6 a.

- b. The binary sequence 1100100010 is applied to the DPSK transmitter

- i) Sketch the resulting wave from at the transmitter output.

- ii) Applying this waveform to the DPSK receiver, show that in the absence of noise, the original binary sequence is reconstructed at the receiver output. (06 Marks)

- An FSK system transmits binary data at the rate of  $2 \times 10^6$  bps. During the source of C. transmission, AWGN of zero mean and two sided PSD 10<sup>-20</sup>Watts/Hz is added to the signal. The amplitude of the received sinusoidal wave for digit 1 or 0 is  $1\mu\nu$ . Determine the average probability of symbol error assuming non-coherent detection. (04 Marks)

#### Module-4

- a. Explain the following terms with related equations and diagram with respect to base band 7 transmission.

- i) ISI and Nyquist condition for zero ISI

- ii) Duoldinary signal pulse

- iii) Modified duobinary signal pulse

- iv) **P**artial response signals

- v) Raised cosine spectrum.

- b. Explain the need for precoder in a duobinary signaling. The binary sequence 111010010001101 is the input to the precoder whose output is used to modulate a duobinary transmitting filter. Obtain the precoded sequence, transmitted amplitude levels, the received signal levels and the decoded sequence. (06 Marks)

#### OR

- With a neat diagram, explain the concept of linear traversal filter. (06 Marks) 8 a.

- b. Consider a channel distorted pulse x(t), at the input to the equalizer, given by

- $x(t) = \frac{1}{1 + (\frac{2t}{T})^2}$  where 1/T is the symbol rate. The pulse is sampled at the rate 2/T and

equalized by a zero-forcing equalizer. Determine the coefficients of a five-tap zero-forcing (06 Marks) equalizer. (04 Marks)

C. Write a note on eya diagram.

#### Module-5

With a neat cingram explain the generation of PN sequences and state its properties. 9 a

(06 Marks) A DS spread-spectrum signal is designed so that the power ratio  $P_R/P_N$  at the intended b. receiver is  $10^{-2}$ . If the desired  $E_b/N_0 = 10$  for acceptable performance, determine the minimum value of the processing gain. (04 Marks)

Explain with neat block diagram FH spread -spectrum system. (06 Marks С.

## OR

| 10 | a. | (06 Marks)                                                       |            |

|----|----|------------------------------------------------------------------|------------|

|    | b. | Write a note on application of spread spectrum in wireless LANs. | (04 Marks) |

|    | с. | With a meat block diagram, explain the IS-95 reverse link.       | (06 Marks) |

\* \* \* 2 of 2 \* \* \*

| USN | N        |                                                                                                                                                          | 15EC62                                 |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|     |          | Sixth Semester B.E. Degree Examination, June/July 2019<br>ARM Micro Controller and Embedded Systems                                                      | i.                                     |

| Tii | me:      | 3 hrs. Max. M                                                                                                                                            | arks: 80                               |

|     |          | Note: Answer any FIVE full questions, choosing<br>ONF full question from each module.                                                                    |                                        |

|     |          | Module-1                                                                                                                                                 |                                        |

| 1   | a.<br>b. | Explain the architecture of ARM cortex – M3 processor with neat diagram. With neat diagram, explain operation mode and privilege levels in cortex M3.    | (08 Marks)<br>(08 Marks)               |

|     |          | OR                                                                                                                                                       |                                        |

| 2   | a.<br>b. | What is stack? Explain push and pop operation. With the help of a neat diagram. Explain in detail special registers used in ARM cortex M3 processor.     | (07 Marks)<br>(09 Marks)               |

|     |          | Module-2                                                                                                                                                 |                                        |

| 3   | a.       | Write an ALP to calculate the sum of 1 to 10 numbers.                                                                                                    | (08 Marks)                             |

|     | b.<br>с. | Explain the following instruction set : i) BFC ii) SBFX iii)ASR iv) MRS.<br>Explain how CMSIS provides standard access. Interface for Embedded software. | (04 Marks)<br>(04 Marks)               |

|     |          | OR                                                                                                                                                       |                                        |

| 4   | a.       | Write a program to blink a LED using 'C' language.                                                                                                       | (08 Marks)                             |

|     | b.<br>с. | Explain the following assembler directives AREA, ENTRY, DCB, ALIGN. Explain different bus interfaces supported by cortex M3.                             | (04 Marks)<br>(04 Marks)               |

|     |          | Module-3                                                                                                                                                 |                                        |

| 5   | a.       | Explain how embedded system are classified.                                                                                                              | (08 marks)                             |

|     | b.       | With neat block diagram, explain the element of embedded system.                                                                                         | (08 Marks)                             |

|     |          | OR                                                                                                                                                       |                                        |

| 6   | a.       | Differentiate between RISC and CISC.                                                                                                                     | (04 Marks)                             |

|     | b.       | Explain how program memory are classified.                                                                                                               | (08 Marks)                             |

|     | С.       | Explain how brown-out protection circuits works.                                                                                                         | (04 Marks)                             |

|     |          | Module-4                                                                                                                                                 |                                        |

| 7   | a.       | What are the operational and nonoperational attributes of an embedded systems.                                                                           | (10 Marks)                             |

|     | b.       | Explain different types of serial interface bus used in automotive communication.                                                                        | (06 Marks)                             |

|     |          | OR                                                                                                                                                       |                                        |

| 8   | a.<br>b  | Explain fundamental issues in hardware software co-design.                                                                                               | (06 Marks)                             |

|     | b.       | Explain with a neat block diagram how source file to object file translation take pl                                                                     |                                        |

|     | C.       | Explain super loop based approach of embedded firmware design.                                                                                           | (06 marks)<br>(04 Marks)               |

|     |          |                                                                                                                                                          | ······································ |

1 of 2

Important Note : 1. On completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages. 2. Any revealing of identification, appeal to evaluator and or equations written eg, 42+8 = 50, will be treated as malpractice.

CBCS SCHEME

1990

1992

-

190

# 15EC62

(08 marks)

(04 marks)

## Module-5

- 9 a. With neat diagram explain operating system architecture.

- b. Explain how operating systems are classified.

- c. Differentiate between hard real time system and soft real time system with an example for each. (04 Marks)

# **@**R

- 10 a. With neat diagram, explain embedded system development environment. (08 marks)

- b. For the following jobs calculate the tumaround time, waiting time using preemptive SJF scheduling algorithm. (04 Marks)

| Jolls | CPU bust time | Arrival time |

|-------|---------------|--------------|

| 1     | 10            | 0.0          |

| 2     | 2             | 3.0          |

| 3     | 1             | 4.0          |

| 4     | 4             | 5.0          |

c. Write a note on IAP [In Application Programming] and in system programming. (04 Marks)

(08 Marks)

3 a. Write the lambda based design rules for separation of layers and transistors. (06 Marks)

b. Draw circuit, stick and layout diagram for nMOS shift register cell. (10 Marks)

# OR

a. Define sheet resistance (R<sub>s</sub>) standard unit of capacitance (□Cg) and delay unit (τ) (06 Marks)

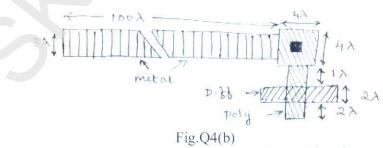

b. Calculate the capacitance of the structure given below in Fig.Q4(b). (10 Marks)

Area capacitance value for metal 1 to substrate  $= 0.3 \text{pF} \times 10^{-4}/\mu\text{m}^2(0.075 \text{ relative value})$ Area capacitance value for diffusion to substrate  $= 1 \text{pf} \times 10^{-4}/\mu\text{m}^2(0.25 \text{ relative value})$ Area capacitance value for polysilicon to substrate  $= 0.4 \text{ pF} \times 10^{-4}/\mu\text{m}^2(0.1 \text{ relative value})$ .

2. Any revealing of identification, appeal to evaluator and /or equations written cg. 42+8 = 50, will be treated as malpractice. Important Note : 1. On completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages.

4

1 of 2

- Obtain the scaling factor for the following device parameters : 5 a.

- i) gate capacitance

- ii) gate area

- iii) saturation current (Idss)

- iv) channel resistance (Ron)

- v) maximum operating frequency  $(f_0)$

- vi) power dissipation per gate (Pg)

- vii) current density (J)

- viii) gate delay (T<sub>d</sub>).

- b. With a neat diagram explain  $4 \times 4$  Barrel shifter.

(08 Marks) (08 Marks)

#### OR

| 6 | a. | Explain the general arrangement of a 4 bit data path for processor. | (08 marks) |

|---|----|---------------------------------------------------------------------|------------|

|   | b. | Describe Mancllester carry chain element.                           | (08 Marks) |

## Module-4

| 7 | a. | Discuss the architectural issues to be followed in the design of VLSI sub system. | (05 Marks) |

|---|----|-----------------------------------------------------------------------------------|------------|

|   | b. | Explain in detail the general structure of an FPGA fabric.                        | (06 Marks) |

- b. Explain in detail the general structure of an FPGA fabric.

- c. Explain switch logic implementation of CMOS 5 way selector with neat circuit diagram.

(05 Marks)

#### (CR

| 8 | a. | Explain the structured design approach for the implementation of a parity generator. |            |  |

|---|----|--------------------------------------------------------------------------------------|------------|--|

|   |    |                                                                                      | (08 marks) |  |

|   | b. | Explain dynamic CMOS logic with example.                                             | (08 Marks) |  |

## Module-5

| 9 | a. | Explain 3 transistor dynamic RAM cell with schematic diagram. | (06 Marks) |

|---|----|---------------------------------------------------------------|------------|

|   | b. | Explain any two fault models in combinational circuits.       | (06 Marks) |

|   | C. | Write a note on automatic test pattern generation.            | (04 Marks) |

## OR

| 10 | a. | write short notes on :                                      |            |

|----|----|-------------------------------------------------------------|------------|

|    |    | i) observability and controllability                        |            |

|    |    | ii) Built In Self Test (BIST).                              | (08 Marks) |

|    | b. | Explain nMOS pseudo static RAM cell with schematic diagram. | (08 Marks) |

2 of 2

\* \* \*

|   |     |                | CBCS SCHEME                                                                                                                                                                               |                                              |

|---|-----|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

|   | USN | N              |                                                                                                                                                                                           | 15EC64                                       |

|   |     |                | Sixth Semester B.E. Degree Examination, June/July 2019<br>Computer Communication Networks                                                                                                 |                                              |

|   | Tii | me:            | 3 hrs. Max. Mar                                                                                                                                                                           | ks: 80                                       |

|   |     |                | Note: Answer any FIVE full questions, choosing<br>ONE full question from each modula.                                                                                                     |                                              |

|   |     |                | Module-1                                                                                                                                                                                  |                                              |

|   | 1   | a.<br>b.<br>c. | With a neat diagram, explain the responsibilities of each layer in TCP/IP protocol su                                                                                                     | 06 Marks)<br>04 Marks)<br>uite.<br>06 Marks) |

| 1 | 2   | a.<br>b.       | example. (0<br>Explain stop and wait protocol and show how adding sequence numbers can<br>duplicates with the help of flow discussion.                                                    | 8 Marks)                                     |

| - |     |                | Module-2                                                                                                                                                                                  |                                              |

|   | 3   | a.<br>b.       | in CSMA. (0<br>A pure ALOHA network transmits 200-bit frames on a shæred channel of 200kbps.<br>through put if the system (all stations together) produces?<br>i) 1000 frames per second? | 8 Marks)                                     |

|   |     | C.             |                                                                                                                                                                                           | 4 Marks)<br>4 Marks)                         |

| 5 |     |                |                                                                                                                                                                                           |                                              |

|   | 4   | a.<br>b.       | lengths? (0<br>Identify if the following Ethernet MAC addresses are unicast, multicast or broadcast<br>i) 47 : 20 : 1B : 2E : 08 : EE<br>ii) EE : FE : 10 : 01 : 11 : 00                  | 7 Marks)                                     |

|   |     | c.             | What are the two effects of the bridges on an Ethernet LAN? Explain with a neat of                                                                                                        |                                              |

| 5 | a. | With a neat diagram, explain two types of networks defined in Bluetooth. | (04 Marks) |

|---|----|--------------------------------------------------------------------------|------------|

|   |    | What is hidden station problem in wireless LAN's? Give solution for it.  | (06 Marks) |

|   | C. | Describe WLAN. How is it used in grouping of stations?                   | (06 Marks) |

1 of 2

Important Note : 1. On completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages. 2. Any revealing of identification, appeal to evaluator and /or equations written eg. 42+8 = 50, will be treated as malpractice.

- 6 a. Explain the occupation of the address space in classful addressing. (04 Marks)

- A block of addresses is granted to a small organization. We know that one of the addresses is 167.199.170.82/27. What is the first address, last address and total number of address of the block? (06 Marks)

- c. With a neat diagram, explain how can a NAT help in address translation. (06 Marks)

7 a. With a neat diagram explain 1PW4 datagram format? (08 Marks)

b. What is the two addresses approach in mobile host? Explain the significance of home agent and foreign agent with a diagram. (08 Marks)

## OR

- 8 a. With relevant diagrams describe Distance Vector Routing. What is two node instability in DVR? (10 Marks)

- b. Explain operation of Border Gateway Protocol (BGP) with a diagram. (06 Marks)

## Module-5

- 9 a. Explain connection less and connection oriented service showing the movement of packets using time line. (08 Marks)

- b. Explain why the size of the send window in Go back N must be less than  $2^{m}$ ? (08 Marks)

## OR

- 10 a. Explain TCP connection establishment and connection termimation using three way hand (10 Marks)

- b. Describe slow start algorithm for handling congestion in TCP. (06 Marks)

- Derive the Erlang's lost call formula with iterative application of recurrence relation. a.

- b. A group of 20 trunks provides a grade of service of 0.01 when offered 12E of traffic. How much is the grade of service improved if 2 extra trunks are added to the group? How much does the grade of service deteriorates if one trunk is out of service? (07 Marks)

(09 Marks)

#### OR

Design a grading for connecting 20 trunks to switches having ten outlets. a. (08 Marks) Derive the expression for minimum number of cross points in a three stage network with M b. incoming trunks and N outgoing trunks for (M > N) case. (08 Marks)

#### Module-4

| a. | Explain Time-Space-Time switch with suitable diagram.                           | (08 Marks) |

|----|---------------------------------------------------------------------------------|------------|

| b. | Explain synchronization and frame alignment of PCM signals in digital exchange. | (08 Marks) |

|    | OR                                                                              |            |

| a. | Briefly explain basic software architecture of a DSS.                           | (08 Marks) |

| b. | With the help of features flow diagram, explain call forwarding feature.        | (08 Marks) |

|    | Module-5                                                                        |            |

| a. | Describe the various organizational interfaces of DSS central office.           | (10 Marks) |

| b. | Briefly explain strategy for improving software quality with diagram.           | (06 Marks) |

|    | OR                                                                              |            |

10 a. Explain generic switch hardware architecture with neat diagram. (08 Marks) Write short note on : i) Reliability analysis ii) Recovery strategy. b. (08 Marks)

\* \* \* \* \*

2. Any revealing of identification, appeal to evaluator and /or equations written cg, 42+8 = 50, will be treated as malpractice. Important Note : 1. On completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages.

6

7

8

9

Important Note : 1. On completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages.

6

a. Briefly explain programmable array logic. (08 Marks)

b. Explain signal integrity issue in PCB design and also explain measures to reduce these issues. (08 Marks)

1 of 2

(08 Marks)

(08 Marks)

# Module-4

- 7 a. Explain the serial transmission of 64 bit data within clock domain with timing diagram. (08 Marks)

- b. Explain the following serial interface standards for connecting I/O devices.

i) RS232 ii) Fire wire. (08 Marks)

## OR

8 a. Explain any 4 analog sensors.b. Explain the concept of multiplexed buses

## Module-5

9 a. Explain logical partitioning and physical partitioning of a transport monitoring system.

|    | A1                                        | 1 | (08 Mark | (s) |

|----|-------------------------------------------|---|----------|-----|

| b. | Explain fault model and fault simulation. |   | (08 Mark | (s) |

#### OR

10 a. Explain 4 bit LFSR and CFSR for generating pseudorandom test vectors.(08 Marks)b. Explain briefly area, power and timing optimization in digital circuits.(08 Marks)

2 of 2